インテルがチップレット接続の標準化を画策、小さなチップレットを多数つなげて性能向上を目指す インテル CPUロードマップ

前回はISSCC 2025におけるGranite Rapids-Dの発表を説明したが、ISSCC 2025でインテルはもう1つ発表している。今回はそのもう1つの発表であるPaper 2.4 "300MB SRAM, 20Tb/s Bandwidth Scalable Heterogenous 2.5D System Inferencing Simultaneous Streams Across 20 Chiplets with Workload-Dependent Configurations"を説明しよう。

メニーコア・プロセッサーを定期的に発表するインテルが チップレット接続の標準化を画策

インテルは定期的に、複数コアのプロセッサーを作っては発表している。筆者が知る限り最初のものは、Tera-Scale Computingという研究プロジェクトに基づいたもので、連載314回で説明した80コアでTFlops級のプロセッサーであり、2007年のISSCCでは性能のレポートもされている。

2006年のIDFで発表された80コアのチップ

この研究に直接関係しているかどうかはともかく、インテルはこの後Larrabeeを開発。これは製品化せずに、この後継のKnight FerryにIntel MIC(Many Integrated Core)アーキテクチャーと名付けた上で、Xeon Phiというブランドで商品化する。この後も、ISSCCではちょくちょく多数のコアを集積したプロセッサーを作っては発表することがあり、今回もその1つと言えなくもないが、大きな違いはチップレットを前提にしていることだ。

今回の動機は、すでにチップレットが実用段階に入っており、この先はさらに多様多種の工場で製造するさまざまな種類のチップレットを組み合わせることが想定されるとした上で、このチップレットの接続を標準化したい、というものだ。

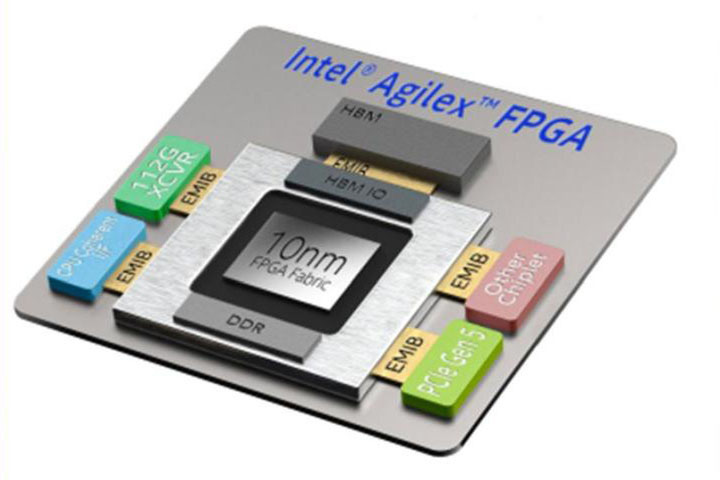

実用段階のチップレット。ここでSapphire Rapidsを持ってこないあたりが良心的。ちゃんと機能分割したチップレット製品でないと意味がないことをわかっている

ここに出てくる例はあくまでも"Example"だとするが、左のConfig 1はL4搭載のMeteor Lakeを彷彿とさせる。やはり社内ではそれなりに開発が進んでいて、最後にキャンセルになったという話なのかもしれない

もっとも標準化といっても「なにを」という話が付きまとう。この研究では標準化の種類について以下の7項目を挙げたうえで、そのうちのInter chiplet networkとCo-design of base die and top diesの2項目に関して標準化案の叩き台となるような構造を設計・試作したという話である。

- Host Interface

- Inter chiplet network

- Co-design of base die and top dies

- Package

- Assembly

- Testing

- Software

その叩き台の構造が下の画像である。要するに碁盤の目のように区画を作り、そこにさまざまなチップレットを目的に応じて配することで柔軟性を確保しようというものだ。

別にこれなら2.5Dのシリコン・インターポーザーでいいじゃないかという声も出そうで、実際CoWoSでこれが簡単に実現できる。ところがインテルのEMIBはこういうことができないので、3DのFoveros的な構造を前提にしないといけない。もうこのあたりからこの叩き台が破綻している気がしなくもない

基本的な構造がFoveros的な3D Packageを前提にしているが、TSMCのSoICと異なりコンピュートタイルとメモリータイル、アクセラレータータイルを縦に積み重ねることはせず、あくまでもこうしたタイルは2次元的に配置、チップレット間の配線はベースタイル側に置き、その間をマイクロバンプで接続する仕組みになっている。連載812回で取り上げたTSMCのSoICにもあったが、こうした2次元方式の接続は配線距離が長くなりがちだし、マイクロバンプを使うと配線密度を上げられないし配線抵抗も多い。

ただ今回の目的は、そうでなくても実装コストが上がりがちなチップレットを低コストで利用できるようにするとともに、構成の自由度を上げることでTime to Marketまでの時間を短縮するのが目的であり、性能に関して言えばヘテロジニアス構成の分散コンピューティングという「仕組みで性能を上げる」方向性を志向しており、個々のコンピュートタイルの性能を引き上げるのには適していないので、これで良しと判断したのかと思われる。

とはいってもこれはあくまでも叩き台なので、まずはTile-to-Tileに汎用的に使える(というのがConfigurableの意味と思われる)ネットワークの構築と、その上で本当に複数のチップレットを並行して動作させるための仕組み作りにフォーカスしたとしている。なお、インテルの説明はタイルとダイを混在させているので、本稿は全部タイルに統一して説明する。

実際のベースタイルとコンピュートタイル、メモリータイルの構造が下の画像だ。細かい寸法は後で出てくるが、タイルの大きさはおおむね4mm角になっている。ただ実際にはD2D I/FやGPIOなども入っているので、コンピュートエンジンなりメモリーなりを搭載できる領域は2×2mmくらいとそれほど大きくない。

ベースタイルは最大で25個のタイルを載せられる格好。一方上に載せるタイルは1×1/1×2/1×4と3種類の大きさが想定されている。基本となるのがCS(Chipset Slot)という単位なのだそうだ

もっとも今回は研究プロジェクトなので、端的に言えば動けばいいという話でもあり、そこまで絶対的に高い性能が必要なわけではなく、性能/消費電力比や性能/タイル面積といったものがきちんと測定できれば良いという割り切りは当然あったのだろう。