前世代の課題を解決し、最新プロセスで性能強化したPanther Lake

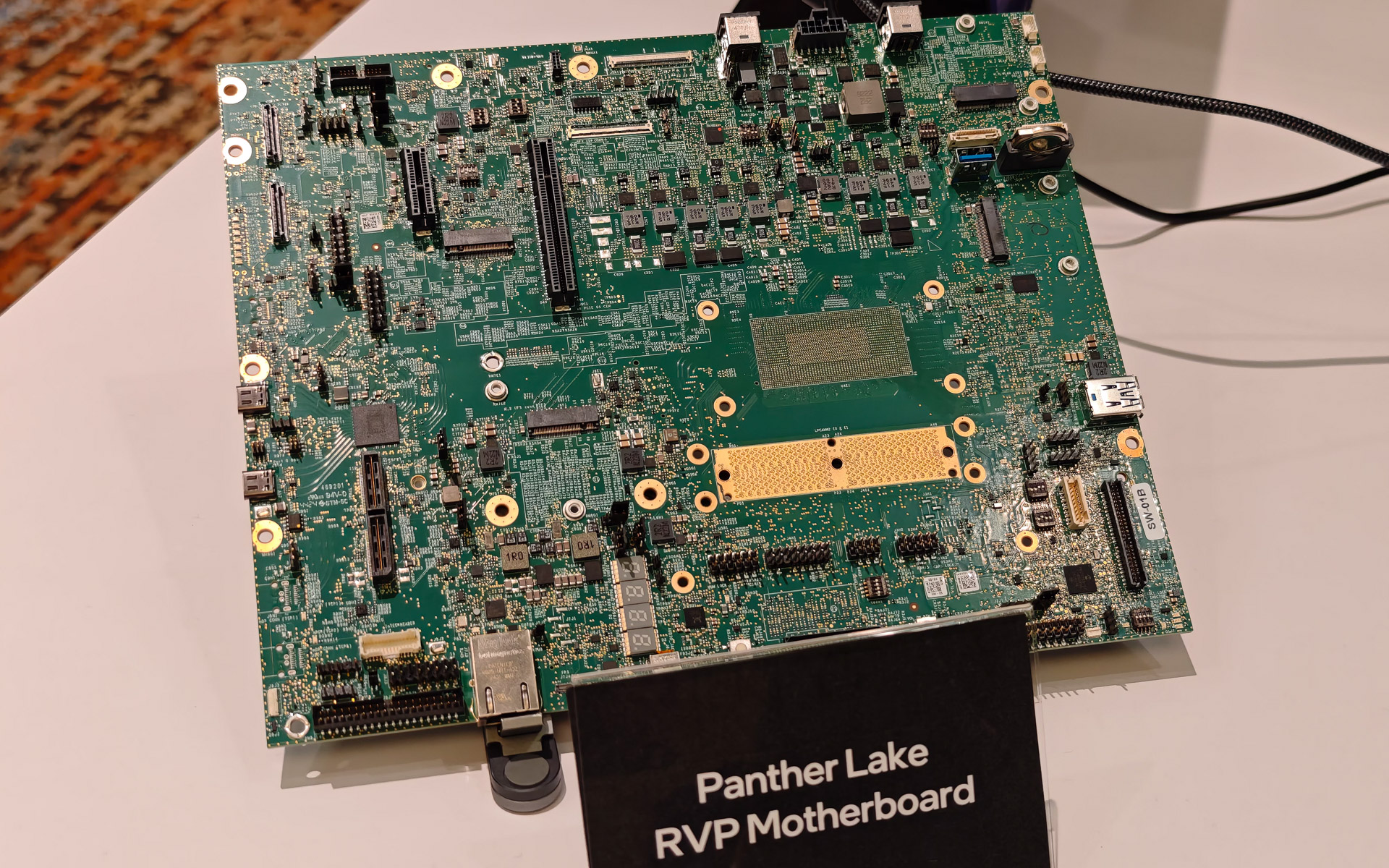

Intelは、次期CPUのCore Ultraシリーズ3となるPanther Lake(開発コードネーム)の技術概要を発表した。詳細に関しては別のニュース記事をご参照いただくとして、本レポートではPanther Lakeの技術概要の解説を行なっていきたい。

今回のPanther Lakeにおいて、Core Ultraシリーズ2で2つに分離してしまったパッケージを再び1つに統一するという役割があるほか、CPUを改良し、GPUとNPUに関しては新しい世代のアーキテクチャを採用することで、電力効率や性能を向上させている。

特にCPUに関しては、マイクロアーキテクチャの進化はわずかだが、Intel 18Aという新しいプロセスノードを採用していることで、性能が10%向上し、電力効率が40%改善されている。

Panther Lakeの技術的な概要に関しては以下のニュース記事に詳細にまとまっているため、それぞれIntelが発表したことに関する詳しいことを知りたいという読者の皆さまには以下の記事をご参照いただきたい。

Panther Lakeの最大の意義は、Lunar LakeとArrow Lakeという2つのCore Ultraシリーズ2の「伏線を回収」することだ。その伏線とはLunar LakeとArrow Lakeで分かれてしまったパッケージを統一することである。

IntelはCore Ultraシリーズ2世代で、Lunar LakeをモバイルノートPCの中でもハイエンド、Arrow Lakeを薄型ゲーミングノートPCの中のハイエンド(Hシリーズ)、またはモバイルノートPC向けのメインストリーム(Uシリーズ)として位置づけてきた。

Lunar LakeはMoP(Memory on Package)のBGA2833と呼ばれるパッケージで、メインメモリ(LPDDR5x)を混載。一方Arrow LakeではMeteor Lakeと同じBGA2049パッケージになっており、メインメモリは普通にメインボード上に搭載されていた。そもそも外部にメモリを接続できないLunar Lakeと、外部にメモリを接続しなければならないArrow Lakeではピン配置に互換性がなく、メインボードを共通化できなかった。

MoPが性能や電力管理の点で大きな意味があることは議論の余地がない。しかし、その反面、コストと在庫管理、メインストリーム向けのArrow Lakeと別の基板を作らないといけないことは、Intel自身にとって、そしてPCメーカーにとっては大きな課題になってしまった。

Intelにとっての課題は、自身が製造していないDRAMを外部のDRAMメーカーから購入しなければならないこと。後工程のLunar Lakeを組み立てる段階で、十分な数の在庫を持っていないといけないため、不必要な在庫が積み上がる、あるいは逆に在庫が足りなくて十分な数を製造できないという課題に直面することになる。

PCメーカーにとっての課題は、メインボードの設計と製造コストだ。Lunar Lake、Arrow Lakeと2種類のパッケージがあるため、PCメーカーは2つのメインボードを設計し、製造し、在庫の管理をする必要がある。こうすると、設計と在庫管理のコストがかさむことになるため、PCメーカーにとっては単なるコストアップになってしまう。

それに対して競合のAMDやQualcommはいずれも1つのパッケージでローエンドからハイエンドまでカバーしている。

AMDはRyzen AI 300シリーズ(ハイエンドがStrix Point、メインストリームはKracken Point)とRyzen 200(Ryzen 8040シリーズのリフレッシュ版、Hawk Point)というダイが違う3つの製品をモバイルノートPC向けに提供しているが、すべてFP8という同じパッケージ上で実現しており、ピン互換で1つのメインボードでカバーできる。

QualcommのSnapdragon Xシリーズも同様で、CPUコアが12つのハイエンドと、CPUコアが8つのバリュー向けの2つのダイが用意されているが、パッケージは共通だった。

このように、Intelにとっても、その顧客にとっても課題となってしまっていたこの2つのパッケージ問題、それを解消するのがPanther Lakeの大きな役割だ。

では、Intelはこの2つのパッケージ問題をどのように解決したのだろうか?シンプルに言えば、外部のパッケージは共通だが、CPUコアやGPUコアの数が異なるという展開を行なうことにしている。それを可能にしたのが、IntelがMeteor Lake世代で導入した、Foveros-S(Meteor Lake導入当時はFoverosは1種類しかなかったため単にFoverosと呼ばれていたが、その後Foverosは複数の技術が導入されたため、オリジナルのFoverosはFoveros-Sと呼ばれるようになった)というチップレット技術だ。

Meteor LakeとArrow Lakeで採用されたFoveros-Sでは、ベースタイルと呼ばれる、電気信号を通すためだけの配線が用意されているパッシブダイの上に、コンピュートタイル(CPU)、グラフィックスタイル(GPU)、SOCタイル(メモリコントローラやNPU)、IOタイル(PCI Expressなど)という4つのタイルを積層するという形になっている。ちなみに、Intelではチップレットのダイのことをタイルと呼ぶ。

Lunar Lakeでは、このタイルを2つに減らし、CPU、GPU、NPU、メモリコントローラなどをコンピュートタイル、IOをプラットフォーム・コントロール・タイル(以下PCT)とし、2つのタイルに集約するという変更を行なったが、Foveros-Sを利用してチップレット技術を利用するという大枠は変えなかった。

今回のPanther Lakeでは、そのLunar LakeとMeteor Lake/Arrow Lakeの合わせ技のようなチップレットになっている。Meteor Lake/Arrow Lakeとの大きな違いは、4タイルから3タイルに減っていることで、従来のSOCタイルの機能は性能に関わる部分はコンピュートタイルに移動しており、Wi-Fi、Ethernet、PCI Express、セキュリティなどはPCTへ移動している。このようにSOCタイルの機能が分割されているのがPanther Lakeの特徴だ。

これにより、NPUはコンピュートタイルというPanther Lakeの中でも最も進んだプロセスノードの中に内蔵されるようになり、最新の第5世代NPUを搭載することで50TOPSの性能になり、Arrow Lakeでは満たせていなかったCopilot+ PCの要件である40TOPS以上のNPUを満たせるようになっている。

一方で、GPUはコンピュートタイルから切り離されて、グラフィックスタイルとして単体のタイルとなっている。グラフィックスタイルとコンピュートタイルは、Foveros-Sにより実現されている「Tile2Tile」と呼ばれる、タイル間を同じ物理タイル上にあるかのようにつなぐインターコネクトで接続した。

電気的にはコンピュートタイル上の内部インターコネクト(Scalable Fabric Gen 2)に接続されており、GPUがかつてコンピュートタイル上にあった時とほぼ同じような性能、低遅延で接続できる。

GPUをグラフィックスタイル状に切り離すメリットは、GPUをコンピュートタイルとは別のプロセスノードで製造できることだ。これはコスト面でのメリットだけでなく、市場に合わせてGPUのタイルを切り替えられることを意味する。

今回IntelはGPUタイルを2種類(Xe3の4コア版と12コア版)を用意しているが、4コア版にはIntel 3を、12コア版にはTSMC N3Eを利用して製造しており、そうした製造面での柔軟性や、市場に合わせてアーキテクチャを伸縮できることもメリットだと言える。

このように、Panther Lakeはチップレットの観点で見れば、Meteor Lake/Arrow LakeとLunar Lakeのそれぞれの良い点を継承したチップレット構成になっていると言える。

このように、チップレット構造に関しては大変革となっているが、CPUのマイクロアーキテクチャに関しては「改良版」というのが今回採用されたCougar Cove、Darkmontの評価になるだろう。

Intelは2019年のIce Lake(第10世代Core)で導入したSunny Coveで、製造技術やSoCとCPUのマイクロアーキテクチャを分離する(つまりはIPデザイン化する)ことを決めて以降、2世代に1度、内部のマイクロアーキテクチャを更新し、次の世代ではその改良を行なうという開発戦略をとってきている。Intel自身はそういう戦略だとは言っていないのだが、以下のSunny Cove以降のPコアのスペックを見ればそれは明らかだ。

2019年のSunny Coveと2020年のWillow Coveは、内部のマイクロアーキテクチャのスペックは全く同じで、大きな違いはキャッシュ容量だけだ。同様にGolden Coveでは、デコーダ長、実行ポート、そして整数演算のALUが増やされ、新しいマイクロアーキテクチャが導入されているが、その後継となる、Meteor Lake世代用のRedwood Coveは、キャッシュ容量以外はGolden Coveと同じスペックだ。

Eコアの方も同様で、2021年のGracemontは完全に新しいマイクロアーキテクチャだが、2023年のCrestmontはその改良版という位置づけであることがスペック表を確認するとわかる。このように、Intelは新マイクロアーキテクチャ→改良版→新マイクロアーキテクチャ→改良版というサイクルで、CPUコアを改良していることが分かる。

そして、昨年(2024年)のArrow Lake/Lunar Lake用に投入されたLion CoveとSkymontは、新しいマイクロアーキテクチャに相当するCPUコアとなる。たとえばLion Coveはデコーダが8ワイドになり、アロケーションも8ワイド、リタイアも12ワイドになっており、さらに内部のALUが整数演算は5から6に、浮動小数点演算は3から4に増えている。

また、L0データキャッシュとして48KBが追加され、L1キャッシュも192KBに増え、L2キャッシュもクライアント向けは2.5MB、サーバー向けは3MB(もっともLion Coveを搭載したサーバー版はまだ登場していないが……)に、と増えている。

EコアのSkymontも同様で、デコーダ長、アロケーション長、リタイア長、整数演算ALU、浮動小数点演算ALUのいずれも増えており、内部のマイクロアーキテクチャを大きく変えていることは一目瞭然だ。

では、今回のPanther Lakeに採用されたCougar CoveとDarkmontはどうかと言えば、もう説明する必要はない。ここ数年の傾向と同じように、Cougar Cove/DarkmontはLion Cove/Skymontの改良版というのが位置づけになる。デコーダ長や内部の演算器などの構成は基本的に同じで、改良ポイントは主にフロントエンドのTLBや分岐予測といったあたりで、Intel自身もそういっているように「最適化」を進めたCPUのIPデザインであると言える。

ただ、Lion Cove/Skymontともに、電力効率の面では評価が高いCPUアーキテクチャだ。LPEコアによりアイドル時の消費電力はArm CPU並みに低く、アクティブ時の消費電力もArm CPU並みで、Snapdragon Xシリーズと遜色ないバッテリ駆動時間を実現できていた。同時に、シングルスレッドの性能も高い。そうした意味ではよくできたCPUコアのデザインで、Cougar Cove/Darkmontはそれをさらに改良したものとなる。

一方、Lunar Lakeの課題はPコア×4+LPEコア×4=8コアという、CPUコア数の少なさがあり、マルチスレッド性能がQualcommやAMDに比べてやや低かったという点にあったが、それもPanther Lakeでは16 coreという新しいデザインポイントを用意することでカバーできるようになる。16 coreのタイルは、Pコア×4+Eコア×8+LPEコア×4という16コア構成になっており、Eコアが都合12コアもある計算になる。

マルチスレッド性能では、CPUコアの数がモノを言ってくるので、高効率なEコアが多くあるというPanther Lakeのデザインはマルチスレッド時の性能を大きく引き上げる可能性を秘めている。実際、Intelが公開した性能データを見てもそうした傾向が見てとれるだけに、このあたりは実際の製品が登場したときの性能に期待したいところだ。

注目したいのは、CPUアーキテクチャの大幅改良はないのに、性能が大きく向上していることだ。マルチスレッドに関してはEコアが増えているので当然としても、シングルスレッドでLunar Lake/Arrow Lakeに比較して同じ性能であれば40%電力は少なくなり、同じ電力であれば10%性能が向上するという。アーキテクチャ上の改良がさほどではない以上、これらの多くは最新のプロセスノードであるIntel 18Aから来ていると考えられる。

その意味で、Intel 18Aの非常に優れたプロセスルールを示すショーケースが今回のPanther Lakeであると言えるし、最新プロセスノードを採用することで他社に比べて優位に立つ、かつての状況が戻ってきたとも言える。いずれにせよ、これからIntel Foundryを利用して生産を検討するほかの半導体メーカーにとって注目していい点だと言えるだろう。

GPUの世代に関しては、Arrow LakeのXe-LPG(Xe世代)、Lunar LakeのXe2からアーキテクチャの世代が1つ上がったXe3に進化している。

IntelのXeアーキテクチャでは、GPUの大きな方からGPU全体、レンダースライス、Xeコア、ベクターエンジンの順に1つの塊として定義されており、レンダースライス単位で、あるいはXeコア単位で、演算器を増やしたり減らしたりできるというスケーラブルな構造になっている。

Lunar Lakeに内蔵されていたXe2では、1つレンダースライスには4つのXeコアが内蔵されており、GPU全体で2つのレンダースライスを備えることで、合計8つのXeコアを内包していた。それに対してPanther Lakeでは1つのレンダースライスに対して6つのXeコアがあり、このレンダースライスが2つあることで、最大12のXeコアという形に強化している。

Xeコアが増えると、それに合わせて内蔵されているベクターエンジン、浮動小数点演算・整数演算のALU、AI演算用のXMXが増えることになるため、それだけで演算性能が向上することになる。

なお、今回Intelはこの12Xeコアという構成と、2レンダースライスに2つのXeコアで4 Xeコア、という2つのダイ構成を用意している。前者はTSMC N3Eで、後者はIntel 3のプロセスノードで生産を行なう。このようにダイのバリエーションごとに生産に利用するプロセスノードを分けられることも、グラフィックスタイルをコンピュートタイルから分離したメリットと言える。

一方、Xe3の内部アーキテクチャは、基本的にXe2のそれを継承した形になっている。IntelはXe2世代で、SIMD16の演算を可能にするベクターエンジンを導入している。これは従来のXeでは、8つの浮動小数点演算・整数演算のALUを1つに束ねて、256bit幅のベクターエンジンを構成して、単精度の浮動小数点演算を8つまとめてSIMD型演算を行なうことを可能にしていた(SIMD8と呼んでいる)。

それに対してXe2では16の浮動小数点演算・整数演算のALUを1つに束ねて、512bit幅のベクターエンジンを構成しており、それにより単精度の浮動小数点演算を16まとめてSIMD型演算できるようにしている(SIMD16と呼んでいる)。

どちらも束ね方の問題で、基本的なALU数は同じなのだが、浮動小数点演算時の効率は向上することになるので、結果的に性能向上につながる形となる。

今回のXe3ではそうしたXe2の特徴を引き継いでおり、Xeコア数が増えたことで、結果的にALU数が1,024から1,536に増えていること、またXeコアあたりの共有L1キャッシュの容量は192KBから256KBに増えていて、GPU全体のL2キャッシュも8MBから16MBに倍増していることなどが強化点になり、その点で性能向上を期待できる。

Intelによれば、Lunar Lakeに内蔵されているXe2に比較して50%の性能向上、同じ性能ならば40%の電力削減と明らかにされており、その向上幅は非常に大きいと言える。

NPUに関しては、Lunar Lakeに搭載されていた第4世代NPUから第5世代NPUへと強化になる。この第5世代NPUでIntelは、内部構造を大きく見直し、必要のない部分を削ぎ落とした。

従来の第4世代NPUに比較してMACと呼ばれる浮動小数点+整数演算器の数は同じだが、行列演算を行なうSHAVE DSPやローカルメモリとなるScratchpad RAMは多すぎたと判断されて減らされている。このため、第5世代NPUは第4世代NPUとほぼ同じ性能を実現しながら、ダイ面積あたりの性能は40%ほど向上している。

Copilot+ PC発表以降、すっかり注目される数値として定着した、AI推論時の性能(TOPS=Tera Operations Per Second、1秒間に何兆回)だが、この第5世代NPUは、第4世代NPU(48TOPS)と比較して、2TOPSしか増えていない50TOPSにとどまっている。AMDはこの50TOPSを既に現行世代(Ryzen AI 300シリーズ)で実現しているし、Qualcommの次世代(Snapdragon X2シリーズ)は80TOPSであると先日明らかになったばかりであることを考えると、随分と控えめな性能向上だなというのが多くの人が抱く感想だろう。

しかし、これはわざとそうしたというのがIntelの考え方だ。というのも、Copilot+ PCの要件として考えると、40TOPSを上回っていればよく、かつPCにおいて、現時点ではGPUの方がAI演算にはよく使われているという現状がある。

Intelは昨年のLunar Lakeの技術概要を発表したセッションで、2024年の時点で、CPU、GPU、NPUが利用されている割合を、CPUが35%、GPUが40%、NPUが30%と説明しており、2025年の予測としてそれが30%、40%、35%になると説明している。それが正しいとすれば、依然としてGPUを使うアプリケーションの方が多く、NPUに関しては、Copilot+ PCの要件である40TOPS以上を超えておけば十分だと判断したということだろう。

実際、今回のPanther LakeのGPU(12Xe)は120TOPSと、Qualcommの最新NPUの80TOPSなどを軽く超えており、Adobeのアプリなどがその端的な例だが、NPUよりもGPUを利用するAI処理の方が多いことを考えれば、Intelの考えも十分に根拠がある。

なお、Arrow LakeのNPUは第3世代NPUで13TOPSしかなく、Intelのメインストリーム製品がCopilot+ PCに対応できなかった問題は、今回のPanther Lakeで解決できるようになる。多くのエンドユーザーやPCメーカーにとっては、これがグッドニュースと言えるだろう。

IntelはこのPanther Lakeのチップレットの特徴、CPU、GPU、NPUのIPデザインを生かして、2種類のコンピュートタイル、2種類のグラフィックスタイル、2種類のプラットフォーム・コンピュートタイル(PCT)を用意し、その組み合わせにより「8 core」「16 core」「16 core 12Xe」という3つの種類の構成を用意している。

最もハイエンド構成となるのが16 core 12Xeになる。コンピュートタイルは16コア(4P+8E+4LPE)で、グラフィックスタイルは12Xeコア、PCTが12レーンPCIeのPCTとなる。ミッドレンジが16 coreで、コンピュートタイルはCPUは16コア(4P+8E+4LPE)で、グラフィックスタイルは4Xeコア、PCTが20レーンPCIeのPCTとなる。ローエンドの構成は8 coreでコンピュートタイルはCPUは8コア(4P+4LPE)で、グラフィックスタイルは4Xeコア、PCTが12レーンPCIeのPCTとなる。

これだけを見ると、16 core 12XeがArrow Lake-H(Core Ultra 200H)の後継で、8 coreがLunar Lakeの後継と見えるかもしれないが、おそらくそうではないと思う。今回Intelは具体的な製品構成(シリーズ構成やSKU構成など)を一切明らかにしていないので、なんとも言えないのだが、おそらく8 coreはモバイルのメインストリーム向けの構成で、Arrow Lake-U(Core Ultra 200U)の後継となるだろう。

その意味で、Lunar Lakeの後継をどうするかが興味あるところだが、可能性として高いのは、16 Core 12XeのGPUを8Xeコアに減らしたバージョンを用意して(つまり4Xeコアを無効にして8コアにして出荷する)、それをLunar LakeのTDPの枠に収めるようにするというのが現実的かもしれない。もっともこのあたりは、来年のCESだと目されるCore Ultraシリーズ3の正式な発表を待つ必要があると言えるだろう。